### EE 435

### Lecture 31

String DACs

### Review from Last Lecture R-String DAC

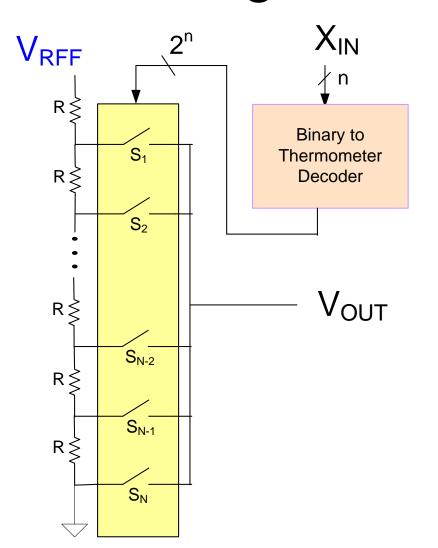

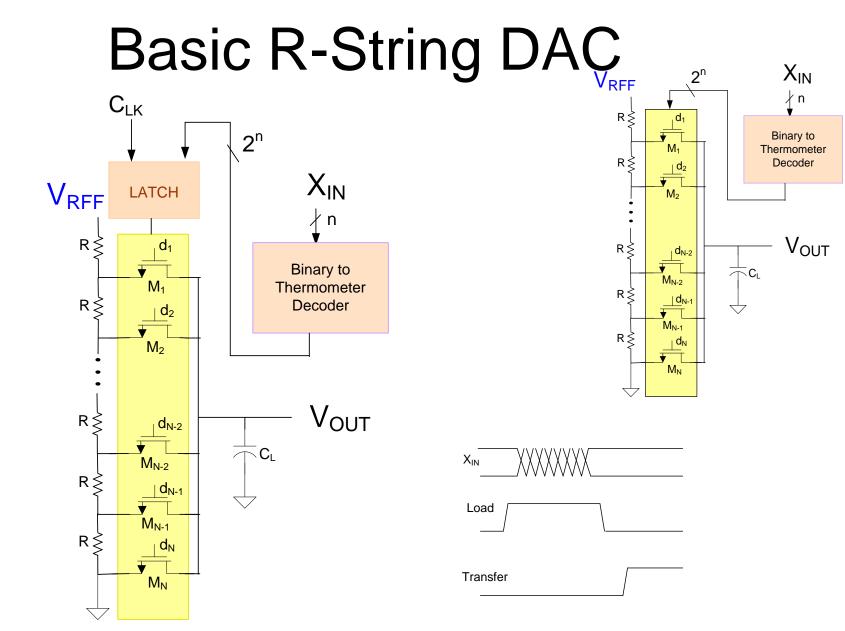

**Basic R-String DAC including Logic to Control Switches**

### Review from Last Lecture R-String DAC

### Review from Last Lecture

**R-String DAC**

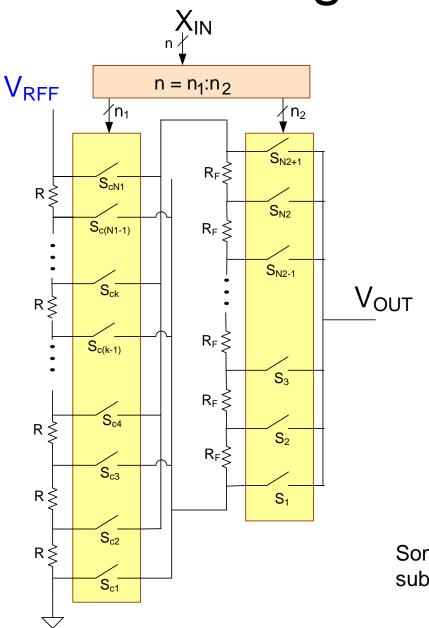

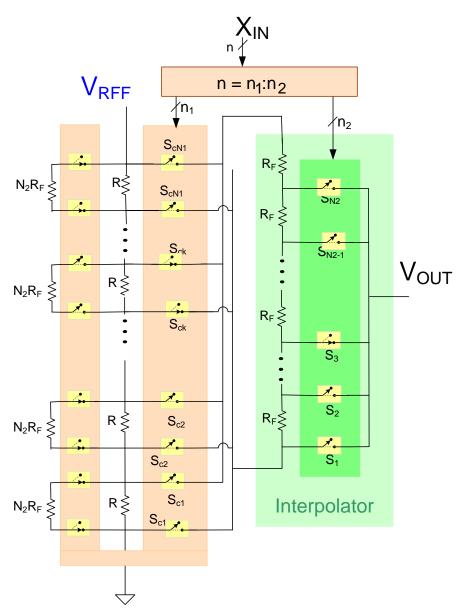

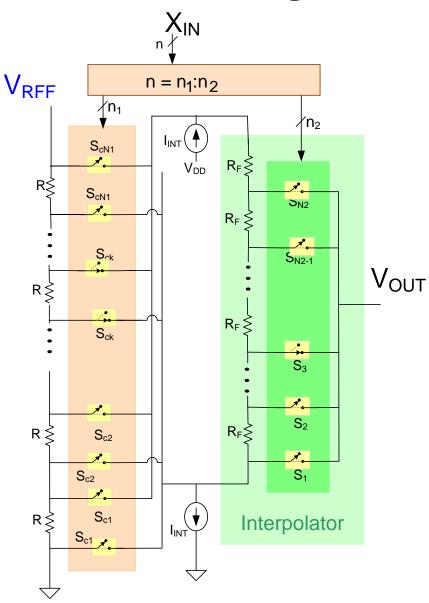

Sometimes termed sub-divider, sub-range or dual-string DAC

Will now look at a classic paper that discusses several key strategies for building string DACs

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 25, NO. 6, DECEMBER 1990

# A 10-b 50-MHz CMOS D/A Converter with 75- $\Omega$ Buffer

MARCEL J. M. PELGROM, MEMBER, IEEE

Though somewhat dated, results are particularly relevant

Most data converter architectures require good matching of a large number of one or more types of components

Some key background information relating to stastical characterization of data converters will be discussed to better understand concepts discussed in this paper

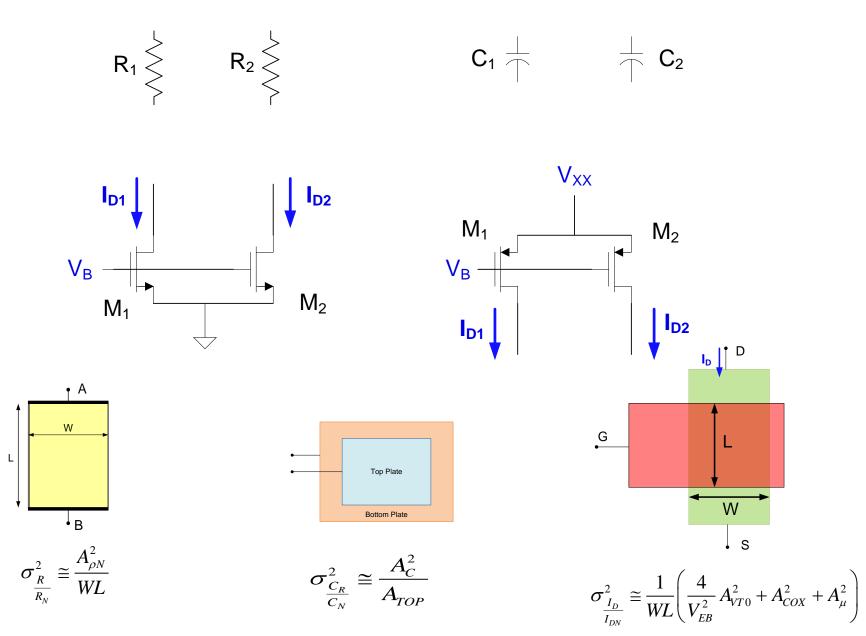

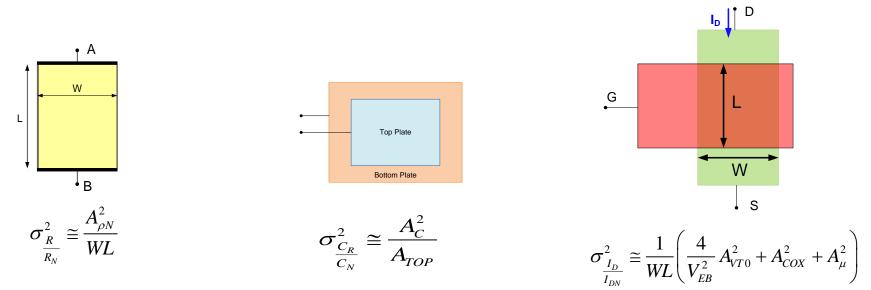

### Matching Properties of Circuit Components

### Matching Properties of Circuit Components

- If edge roughness effects are neglected, standard deviation of components  $\sigma_{\frac{X}{X_{N}}}$  proportional to reciprocal of the square root of area of component

- INL and DNL of most data converters (at low f) depends upon matching characteristics of basic circuit components

- Often INL and DNL proportional to standard deviation of components

- Each additional bit of ENOB generally requires a factor of 2 reduction in σ

Each additional bit of ENOB generally requires a factor of 4 increase in area in matching critical circuits !!

ieee journal of solid-state circuits, vol. 25, no. 6, december 1990

Note Dual Ladder is used !

A 10-b 50-MHz CMOS D/A Converter with 75-Ω Buffer

MARCEL J. M. PELGROM, MEMBER, IEEE

<u>A 10-b 50-MHz CMOS D/A converter with 75-Ω buffer</u> - <u>Get It@ISU</u> MJM **Pelgrom** - IEEE Journal of Solid-State Circuits, 1990 - ieeexplore.ieee.org Abstracf -A 10-b 50-MHz digital-to-analog (D/A) converter is pre- sented which is based on a dual-ladder resistor string. This approach allows the linearity requirements to be met without the need for selection or trimming. The D/A ... <u>Cited by 45</u> - <u>Related articles</u> - <u>Web Search</u> - <u>All 2 versions</u>

Cited by 51 (4/5/10) Cited by 109 (4/5/16) Cited by 94 (4/6/14) Cited by 130 (4/24/19) Cited by 133 (4/4/21)

### A 10-b 50-MHz CMOS D/A Converter with 75- $\Omega$ Buffer

MARCEL J. M. PELGROM, MEMBER, IEEE

Abstract —A 10-b 50-MHz digital-to-analog (D/A) converter is presented which is based on a dual-ladder resistor string. This approach allows the linearity requirements to be met without the need for selection or trimming. The D/A decoding scheme reduces the glitch energy, and signal-dependent switch signals reduce high-frequency distortion. The output buffer allows driving 1 V<sub>pp</sub> to 75  $\Omega$ . The chip consumes 65 mW at maximum clock frequency and a full-swing output signal. The device is processed in a standard 1.6- $\mu$ m CMOS process with a single 5-V supply voltage. Current-based circuits dump the complementary part of the signal current to ground: the power supply current is thereby twice the average signal current. If a two-sided terminated transmission line has to be fed by the highimpedance output of the current cell D/A converter, the current should be doubled to obtain the required output swing. In this case, the power supply current is four times the average signal current. A triple video D/A converter

This paper proposes a trimless 10-b 50-MHz D/A converter based on resistor strings. This D/A converter is well suited to be used together with nearly all reported A/D converters for high speed, as these also use resistor strings to obtain the reference for the comparators. The design improves on the standard single-resistor-string approach by using a dual-ladder architecture [3] in a matrix formation [4], [5]. Several measures have been taken in the ladder to reduce the distortion. The decoding aims at minimizing the number of transistors that switch. The on-chip output buffer allows driving 1  $V_{pp}$  to 75  $\Omega$ . The inherent voltage output allows driving a two-sided terminated transmission line with a better power efficiency than a current cell D/A converter.

#### II. THE CHIP DESIGN

#### A. The Ladder Structure

The voltage dependence and the mutual matching of large-area polysilicon resistors allow the design of a converter with high integral and differential linearity. Basically, the variation in the polysilicon resistance value is determined by its geometry variations: the length and width variations result in local mismatches and the thickness variation gives gradients. Equally sized MOS gates suffer in addition to charge variations in the threshold voltage. However, the design of the D/A converter with a single 1024-tap resistor ladder and sufficiently fast output settling requires tap resistors in the order of  $6-10 \ \Omega$ . The size of such resistors in conventional polysilicon technology is such that accurate resistor matching and consequently linearity become a problem.

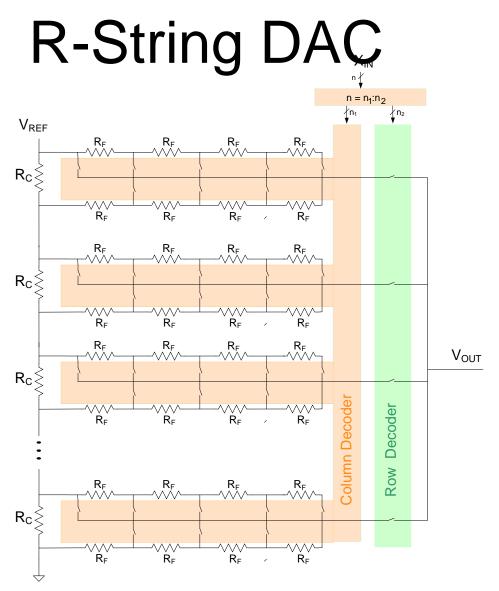

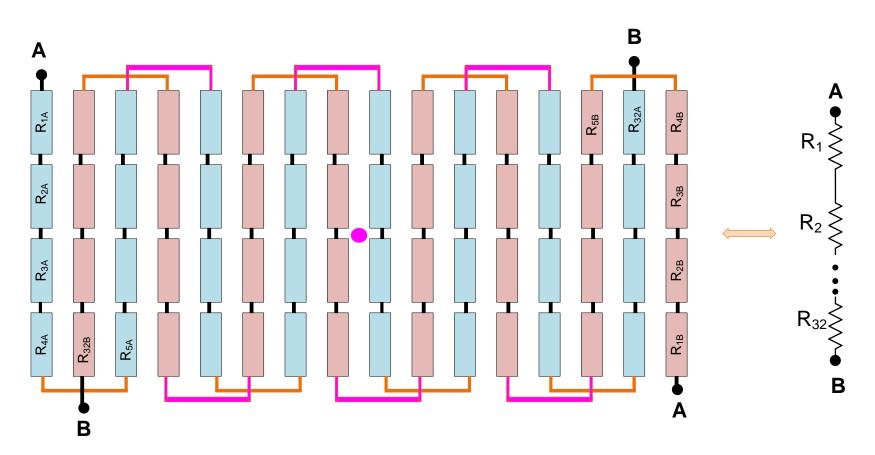

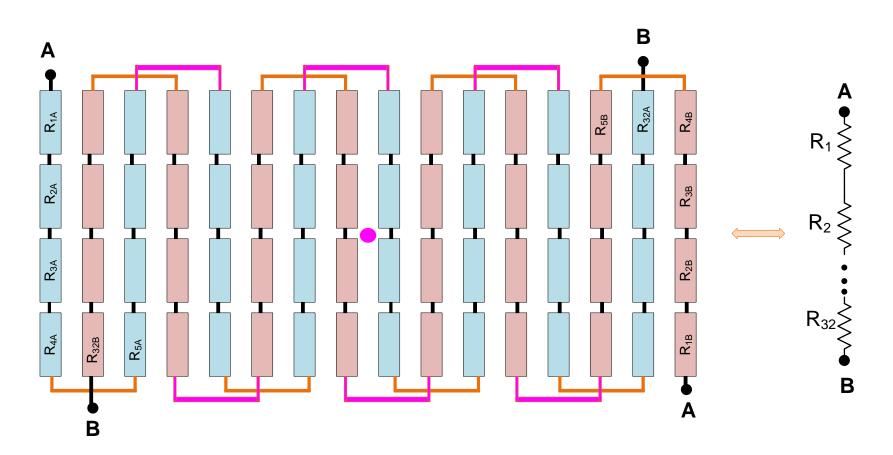

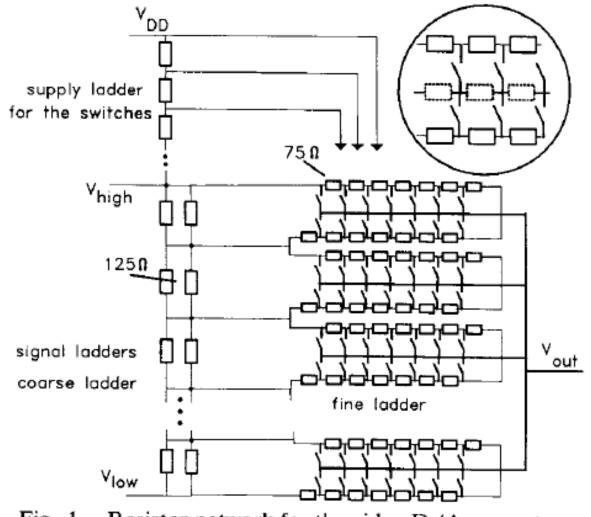

The solution to this problem is the combination of a dual ladder [3] with a matrix organization Randy Geiger Fig. 1 shows the ladder structure. The coarse ladder consists of two ladders each with 16 large-area resistors of 250  $\Omega$ which are connected anti-parallel to eliminate the firstorder resistivity gradient. The coarse ladder determines 16 accurate tap voltages and is responsible for the integral linearity. A 1024-resistor fine ladder is arranged in a 32-by-32 matrix, where every 64th tap is connected to the coarse-ladder taps. This arrangement allows the fineladder tap resistance to be increased to 75  $\Omega$  without loss of speed. The effect of wiring resistances has to be related to the 75- $\Omega$  tap resistors and can therefore be neglected. There are only currents in the connections between the ladders in the case of ladder inequalities: this reduces the effect of contact resistance variance. The current density in the polysilicon is kept constant to avoid field-dependent nonlinearities. The coarse ladder is designed with polysilicon resistors in order to avoid voltage dependence of diffused resistors. The fine ladder is designed either in polysilicon or diffusion, depending on secondary effects in the process implementation.

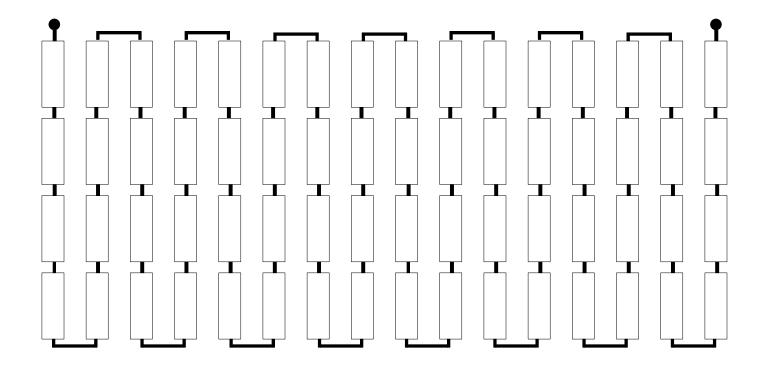

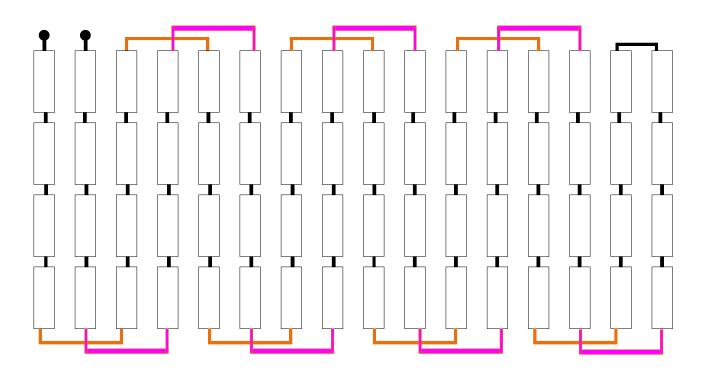

Standard Series Layout of 64 resistors

Layout of 64 resistors with reduced gradient sensitivity

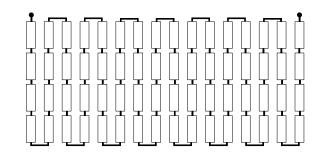

Antiparallel Layout of 32 resistors with Common Centroid

(Pelgrom used only 16 resistors)

Antiparallel Layout of 32 resistors with Common Centroid

Fig. 1. Resistor network for the video D/A converter.

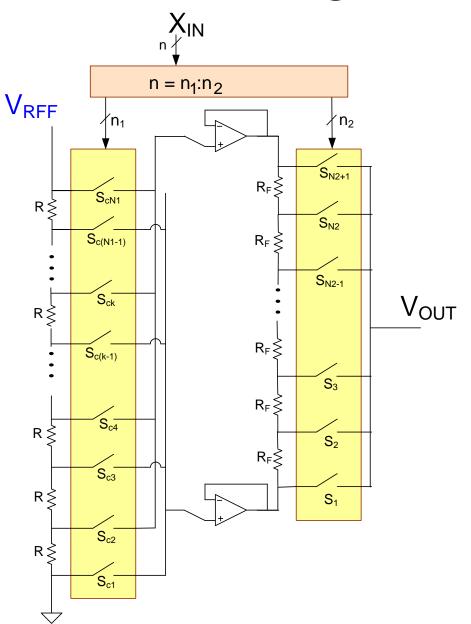

In a basic ladder design consisting of one string of 1024 resistors, the output impedance of the structure varies with the selected position on the ladder and therefore with the applied code. The varying output impedance in combination with the load capacitance results in unequal output charging time and consequently signal distortion. of high-frequency output signals. This source of varying impedance has been eliminated by means of a resistive output rail. The insert in Fig. 1 shows a part of two rows of the matrix. Small resistors are placed in the output rail which connects the switches together. These resistors can be chosen in such a way that any path from the beginning of the resistor row to the end of the output rail shows the same impedance, independent of the chosen switch. This eliminates position-dependent charging of the output rail

and therefore reduces the odd harmonics. In this design, partial cancellation was achieved by placing a unity resistor at the appropriate positions in the output rail. The use of unity resistors keeps the layout simple and does not require additional chip area.

The second source of the varying output impedance is the switch transistor. Usually its on-state gate voltage equals the positive power supply; the voltage on its source terminal, however, is position dependent. The turn-on voltage doubles from one end of the ladder to the other. In this design an additional supply ladder is placed on top of the signal ladders to keep the turn-on voltage of the switches more constant. Effectively the turn-on voltage of each switch transistor is made equal to the lowest turn-on voltage of a basic ladder D/A structure. Therefore there are no additional power supply constraints. For an easy implementation, the switches along each output rail have a common supply line. The variation in turn-on voltage is thereby reduced by a factor of 16. The upper group of switches is fed from the power supply while each lower group is fed with a voltage lowered by one-sixteenth of the maximum signal swing. An additional advantage of this compensation is that the impedance of the switch can be in the order of the total ladder resistance: the switches reduce in width and consequently the clock feedthrough is also reduced.

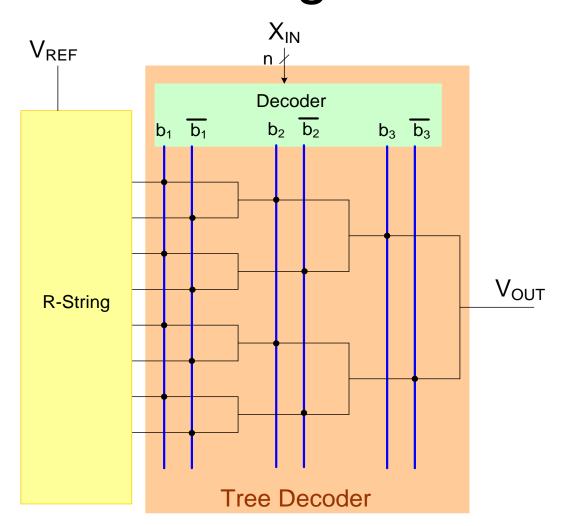

#### B. The Digital Decoder

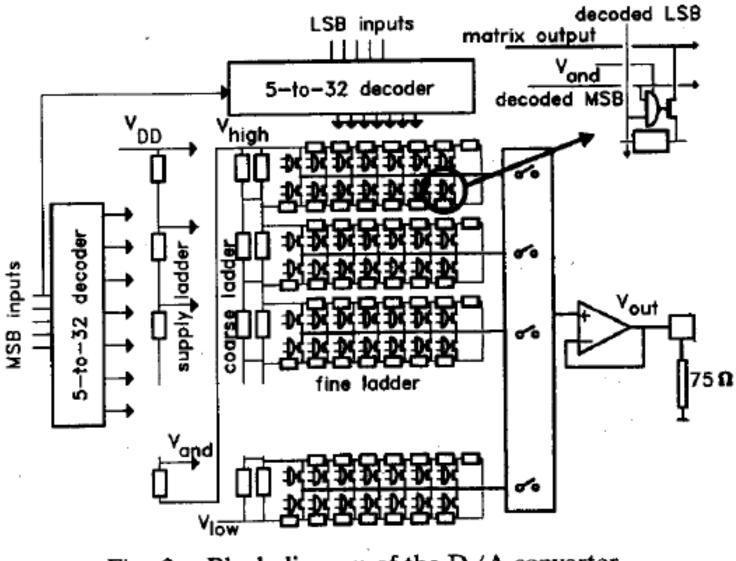

The core of the D/A converter is formed by the 32-by-32 fine-resistor matrix. A switch and a two-input AND gate<sup>1</sup> are connected to each fine resistor to form a basic cell. Two rows of 32 cells each are arranged around one output rail to form one of the 16 sections of the 10-b D/A converter (see Fig. 2). In operation one of the tap voltages of the fine ladder is switched to one of the 16 output rails of the matrix and subsequently to the input of the buffer. In order to select the proper switch, the 10-b digital input word is split in two 5-b words which are decoded by two sets of 5-to-32 decoders, as shown in Fig. 2. The 5-to-32 decoding is performed in two steps: a predecoder converts into ten lines that control 32 threeinput NOR gates of which one gate is activated. In this way minimum capacitive load is driven and maximum speed is achieved. The two decoders are placed on two sides of the matrix. The two sets of 32 decoded lines are latched by the main clock before running horizontally and verti-

Fig. 2. Block diagram of the D/A converter.

.

### Another key paper for matching-critical circuits:

Matching properties of MOS transistors

2401 on Apr 7 2014

3452 on Apr 18 2018

3528 on Apr 17 2019

3745 on Apr 10 2020

3913 Apr 4 2021

Second most cited paper in the IEEE Journal of Solid State Circuits

Most cited basic research paper in IEEE Journal of Solid State Circuits

Latching Boolean Signal Can Reduce/Eliminate Logic Transients which Cause Distortion

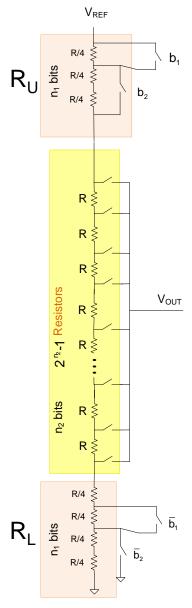

For all  $b_1$  and  $b_2$ ,  $R_U+R_L=R$

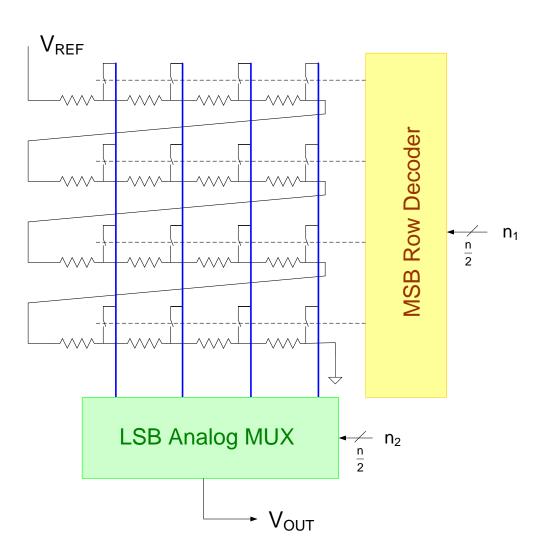

- Another Segmented DAC structure

- Can be viewed as a "dither" DAC

- Often n<sub>1</sub> is much smaller than n<sub>2</sub>

- Dither can be used in other applications as well

# Stay Safe and Stay Healthy !

## End of Lecture 31